APPENDIX A

|

Specifications

of Selected Aircraft SAR Systems |

|||||

|

|

AirSAR |

C/X

SAR |

E-SAR |

KSAR |

STAR-1 |

General |

|

|

|

|

|

|

Country |

USA |

Canada |

Germany |

Denmark |

Canada |

|

Agency |

JPL/NASA |

CCRS |

DLR |

TUD |

Intera |

|

Aircraft |

DC-8 |

CV-580 |

DO-228 |

Gulfstream |

Cessna |

|

Nominal altitude (km) |

8 |

6 |

3.5 |

12.5 |

10 |

|

Nominal airspeed (m/sec) |

- |

130 |

70 |

300 |

145 |

|

Purpose (Experimental or Operational) |

E |

E |

E |

E |

O |

Radar |

|

|

|

|

|

|

Band |

C, L,

P |

X, C |

X, C,

L |

C |

X |

|

Wavelengths (cm) |

5.6,

23.5, 68 |

3.2,

5.6 |

3.1,

5.6, 23 |

5.6 |

3.1 |

|

Frequency (GHz) |

5.3,

1.25, 0.44 |

9.3,

5.3 |

9.6,

5.3, 1.3 |

5.3 |

9.6 |

|

Antenna length (m) |

1.3,

1.6, 1.8 |

-1.2 |

0.15,

0.24, 0.85 |

1.2 |

1.2 |

|

Antenna motion controller |

N |

Y |

N |

Y |

Y |

|

Polarization diversity |

Full |

Full |

HH, VV |

VV |

HH |

|

Quadrature polarization |

C, L,

P |

C |

N |

N |

N |

|

Incident angle (degrees) |

20 -

60 |

0 - 85 |

15 -

60 |

20 -

80 |

45 -

80 |

|

Slant range resolution (m) |

7.5

(S) |

6-20 |

2 (S) |

2, 4,

8 |

6, 12 |

|

Range cells |

- |

4096 |

2048 |

8192 |

4096 |

|

Azimuth resolution (m) |

2 |

<1-10 |

2 |

2, 4,

8 |

6 |

|

Looks |

4 |

1 - 7 |

1 - 8 |

2 - 16 |

7 |

|

Swath width (km) (Slant) |

7 - 13 |

18 -

63 |

3 (S) |

9 - 48

(S) |

40, 60

(S) |

|

Noise equivalent s° (dB) |

- |

-30,

-40 |

-40,

-30, -35 |

-42 |

-30 |

APPENDIX B

MOROCCO

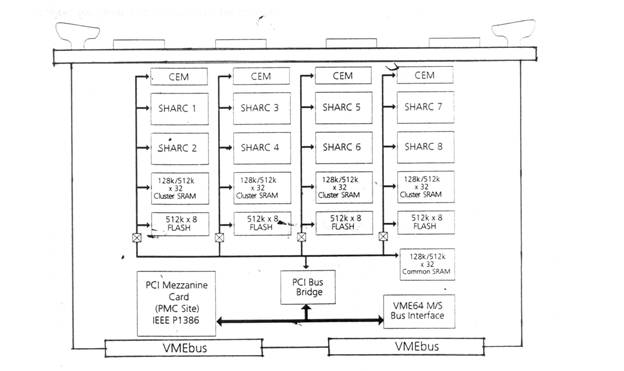

(Octal SHARC VME64

Master Board)

The Morocco board is based on Analog

Devices SHARC™ (ADSP2106x) DSPs.

Digital Signal Processors

Each

SHARC DSP is capable of 120 MFLOPS peak performance and includes a large bank

of on-chip SRAM (up to 4 Mbits). The memory is dual ported to support internal

DMA engines which concurrently drive the six 40 MBytes/s link ports and 240

MBytes /s parallel bus.

Architecture

The

board is architected with a base configuration of four clusters of two SHARCs

each having access to their own cluster SRAM. Each cluster and the PCI bus has

access to a block of common SRAM. On-chip multi-processing arbitration allows

each cluster of ADSP2106xs to share access to cluster SRAM and to arbitrate for

common SRAM or the PCI bus. Large blocks of data can stream into the common or

cluster SRAM from VME64 or the PMC module site. Cluster Expansion Modules (CEM)

can enhance the capabilities of each cluster with additional DSPs, SRAM, DRAM,

or I/O.

Memory

Each

cluster of SHARCs has access to 128k/256k/512k x 32 or zero wait-state cluster

SRAM and, each cluster can have its memory expanded to DRAM, EDRAM or 48-bit

SRAM using the memory options available with CEM.

The

common SRAM is 128k/256k/512k x 32 and is shared with the PCI bus or any one of

the SHARC Clusters.

VME64 Master

VME64

functionality is implemented using the Tundra Universe chipTM. The

Universe chip interfaces VME64 to PCI64 implementing master capabilities on

both busses. The internal architecture of the Universe allows VME64 data

transfer rates close to the theoretical maximum of 80 MBytes/s.

PCI and PMC site

The

Morocco hosts a 32-bit PCI bus with the ability to transfer 132 MBytes/s data

between SHARCs, PMC modules, common and cluster SRAM, and the VME64 bus. The

PMC site is used to host a wide variety of off-the-shelf or custom I/O. Some

examples of PMC modules on the market include high-speed fiber optic and

coaxial interconnects, analog I/O, serial and parallel buses and much more.

Further information for the list of recommended PMC I/O vendors can be

collected from spectrum through www.spectrumsignal.com.

Link Ports

Each

SHARC has six 40 Mbytes/s link ports. Eight link ports, one from each SHARC,

are routed to the front panel. The remaining link ports are interconnected

on-board. Link port 4 is daisy-chained from cluster 0 to all other clusters to

provide an alternative to shared memory VMEbus booting.

Serial Ports

Each

SHARC has two serial ports. One serial port from SHARC is connected to form a

TDM serial bus, which is routed to front panel and to each CEM. The other

serial port from SHARC is routed up to the CEM to control I/O or other SHARCs.

Software

A

complete range of software support is available for the Morocco. Development

tools ar PC hosted with a debugger, C Compiler, optimized signal processing

libraries and DSP operating system support. Support is also provided for host

communications to the SHARCs via an interface library. Device drivers are

available for operating systems such as VxWorks and Solaris.

Features

· Eight 40 MHz on-board SHARC ADSP2106x DSP processors

· 960 MFLOPS (Peak) in a single 6U VME slot

· On-board PCI Local Bus with VME64 to PCI bridge

· One IEEE P1386 standard PCI PMC Site for custom or off-the-shelf I/O

· Four banks of 128k/512k x 32 Cluster 0ws SRAM, each shared between 2 SHARCS

· 128k/512k x 32 Global 0ws SRAM shared with all eight SHARCS

· Cluster Expansion Modules to add memory, I/O, and/or more DSPs

· Comprehensive Software Support

Specifications

·

Motherboard

Format

6U x 160mm VME board

· VME Interface

Tundra Universe VME64

· SHARC Processor

8 ADSP-21060 or ADSP-21062 SHARC processors

120 MFLOP, 40MIPs floating point DSP

240 MBytes/s external memory bandwidth

240 MBytes/s link port bandwidth

10 independent DMA controllers

· SHARC Internal Memory

ADSP-21060: 4MB 0ws dual-ported SRAM

ADSP-21062: 2 MB 0ws dual-ported SRAM

· SHARC External Memory

Cluster SRAM – max 4 x 512K x 32 SRAM

Common SRAM – max 512K x 32 SRAM

CEM DRAM – max 256 MB DRAM

· Expansion Sites

4 CEM sites

1 PMC site

· Connectors

Two 96-pin P1 and P2 VME DIN connectors

8 front-panel SHARC link-port connectors

Front-panel JTAG connector for system debug

Status LED’s

Serial port

· Software

Solaris, Windows NT, and VxWorks drivers

Compatible with ADI software development tools

· Power Requirements

Requires +5V supply only

· Operating Environment

0°C to 70°C

BIBLIOGRAPHY & REFERENCES

·

Ambardar

A.; Analog & Digital Signal Processing; Brooks/Cole Publishing Company,

1999

·

Ausherman

D A, A Kozmer, J L Walker, H M Jones & E C Poggio; Developments in Radar

Imaging; IEEE Trans. on Aerospace and Electronics Systems; Vol AES-20, No.-4,

July 1984; PP 363-400

·

Bonfield D J, J R E Thomas;

Synthetic Aperture Radar Real-Time Processing; IEE Proc. Vol-127, No.-2, April

1980; PP 152-162

·

Brooker; Radar Technology;

Artech House, 1988

·

Brown W M; Synthetic

Aperture Radar; IEEE Trans. on Aerospace & Electronic Systems, Vol AES-3,

No.-2, March 1967; PP 217-229

·

Burrus C S & T W Parks;

DFT/FFT & Convolution Algorithms; John Wiley & Sons, 1985

·

Corrona, Goodman, Majewski;

Spotlight SAR (Signal Processing Algorithms); Artech House, 1995

·

Cavicchi T J; Digital Signal

Processing; John Wiley & Sons Inc., 2000

·

Cook C E; Radar Signals;

Academic Press, 1967

·

Crochier R E, Rabinar L R;

Multirate Signal Processing; Prentice Hall, 1983

·

Curlander J C &

McDonough R N; SAR Systems & Signal Processing; John Wiley & Sons, 1991

·

David Morgan; Surface

Acoustic Wave Devices for Signal Processing; Elsevier Publication

·

Edward A Lee; Programmable

DSP Architectures: Part I; IEEE ASSP Magazine, Octo-1988; PP 4-19

·

Edward A Lee; Programmable

DSP Architectures: Part II; IEEE ASSP Magazine, Jan-1989; PP 4-18

·

Elachi C, Bicknell T, Jordan

R L & Nu. C; Space-borne Synthetic Aperture Imaging Radars: Applications,

Techniques & Technology; Proceedings of the IEEE, Vol-70, 1982; PP

1174-1209

·

Fitch J P; Synthetic

Aperture Radar; Springer-Verlag, 1988

·

George L Turin; An

Introduction to Matched Filters; IRE Trans. on Information Theory, 1960; PP

311-329

·

Giorgio Franceshetti; An

Efficient SAR Parallel Processor; IEEE Trans. on AES, Vol AES-27, No.-2, March

1991; PP 343-352

·

Hanselman D, Littlefield B;

Mastering MATLAB 5: A Comprehensive Tutorial and Reference; Prentice Hall, 1998

·

Harger R O; Synthetic

Aperture Radar Systems: Theory and Design; Academic Press, 1970

·

Harris F J; On the use of

Windows for Harmonic Analysis with the Discrete Fourier Transform; Proceedings

of IEEE, Vol-66, Jan 1978; PP 51-83

·

Herrmann O, Rabinar L R,

Chan D S K; Practical Design Rules for Optimum FIR Low Pass Digital Filters;

Bell Systems Tech. J, 52, 1973; PP 769-799

·

Higgins R J; Digital Signal

Processing in VLSI; Prentice Hall, 1990

·

Hovannessian S A;

Introduction to Synthetic Aperture & Imaging Radars; Artech House, 1980

·

Hovannessian S A; Radar

System Design & Analysis; Artech House, 1984

·

Kirk J C Jr.; Discussion of

Digital Processing in Synthetic Aperture Radar; IEEE Trans. on Aerospace &

Electronic Systems, Vol AES-11, No.-3, May 1975; PP 326-337

·

Kirk J C; Motion

Compensation for Synthetic Aperture Radar; IEEE Trans. on Aerospace &

Electronic Systems, Vol AES-11, No.-3, May 1975; PP 338-348

·

Kovaly J J; High Resolution

Radar Fundamentals- Radar Technology; Artech House, 1947

·

Leland B J; Digital Filters

and Signal Processing; Kluvar Academic Publishers, 1996

·

Levanon N; Radar Principles;

John Wiley & Sons, 1988

·

McClellan J H, Burrus C S,

Oppenheim A V, Parks T W, Schafer R W, Schuessler H W; Computer Based Exercises

for Signal Processing using MATLAB

·

Mitra S K, Kaiser J F;

Handbook of DSP; Wiley-Interscience, 1993

·

Mitra S K; Digital Signal

Processing: A Computer Based Approach; Tata McGraw -Hill, 1998

·

Munson D C, Jorge L C; Image

Reconstruction from frequency-offset Fourier Data; Proceedings of IEEE Vol-72,

No.-6, June 1984; PP 661-669

·

Munson D C; A Signal

Processing view of Strip-Mapping Synthetic Aperture Radar; IEEE Trans. on ASSP

Vol-37, No.-12, December 1989; PP 2131-2147

·

Oppenheim & Schaffer;

Discrete-Time Signal Processing; PHI, 1989

·

Papoulis A; Probability,

Random Variables & Stochastic Processes; McGraw-Hill, 1965

·

Patrik Marchand; Graphics

& GUI with MATLAB; CRC Press, 1999

·

Paul Lynn; Digital Signal

Processing with Computer Applications; John Wiley & Sons, 1994

·

Rudra Pratap; Getting

Started with MATLAB 5; Oxford University Press, 1999

·

Skolnik M I; Radar Handbook;

McGraw-Hill, 1970

·

Stimson G W; Introduction to

Airborne Radar; SciTech Publishing Inc., 1948

·

Strum R D & Kirk D E;

First Principles of Discrete Systems and Digital Signal Processing;

Addison-Wesley Publishing Company, 1989

·

Thomas Einstein; Real-time

Synthetic Aperture Radar Processing on the RACE Multicomputer; Application note

203.0, Mercury Computer Systems Inc., 1994

·

Tomiyasu K; Tutorial Review

of Synthetic Aperture Radar (SAR) with Applications to Imaging of the Ocean

Surface; Proceedings of IEEE Vol-66, No.-5, May 1978; PP 563-583

·

Ulaby F T, R K Moore & A

K Fung; Microwave Remote Sensing Volume I, II & III; Artech House, 1986

·

Ulander L M H; Accuracy of

using Point Target for SAR Calibration; IEEE Trans. on AES, Vol-27, No.-1, Jan

1991; PP 139-148

·

Van de Lindt W J; Digital

Technique for Generating Synthetic Aperture Radar Images; IBM J. of Res.

Developments, Sept 1977; PP 415-432

·

Wehner D R; High Resolution

Radar; Artech House, 1987

From Mathworks: (www.mathworks.com)

·

MATLAB User Guide, 1994

·

Signal Processing Toolbox

User Guide, 1994

From Analog

Devices: (www.analog.com)

·

ADSP-21020 User’s Manual

·

ADSP-21020 Assembler Tools

& Simulator Manual

·

ADSP-21000 Family C Tools

Manual

·

ADSP-21000 Family C Runtime

Library Manual

·

Digital Signal Processing

Applications using ADSP-21000 Family Vol. I & II